2024/08/13

- 前回レポートで検討したSimulationモデルを実際に作ってみました。尚Arbitrator回路は修正しています(*1)。

- 全体モデル: top.v

- design.txtに記述するAnalog入力値ですが、下記の様に 1.0V,0.5V,0.0V 印加としました。それぞれのAD変換結果は 16'hFFFF,16'h8000,16'h0000 となる想定です。

TIME VAUXP[0] VAUXN[0] VAUXP[1] VAUXN[1] VAUXP[2] VAUXN[2] 0 1.000 0.000 0.500 0.000 0.000 0.000

initial begin

#(CYC*5) jtag_reset(); // JTAGコントローラ自身のリセット

#(CYC*5) jtag_set_ir(6'b110111); // XADC JTAG DRP選択

// XADC JTAG Reset XADC論理のJTAGによるリセット

#(CYC*5) jtag_set_dr({2'bxx,4'b0010,10'h003,16'h0001});

// CMD, ADDR, DI

// XADC JTAGLOCKED JTAGによるXADC占有

#(CYC*5) jtag_set_dr({2'bxx,4'b0010,10'h000,16'h0001});

// XADC set single cannel mode 変換モード設定

#(CYC*5) jtag_set_dr({2'bxx,4'b0010,10'h041,16'h3000});

// XADC set and read channel VAUXP/N[0] チャネル選択及びRead

#(CYC*5) jtag_set_dr({2'bxx,4'b0010,10'h040,16'h0010});

#(CYC*5) jtag_set_dr({2'bxx,4'b0001,10'h010,16'hXXXX});

// XADC set and read channel VAUXP/N[1] チャネル選択及びRead

#(CYC*5) jtag_set_dr({2'bxx,4'b0010,10'h040,16'h0011});

#(CYC*5) jtag_set_dr({2'bxx,4'b0001,10'h011,16'hXXXX});

// XADC set and read channel VAUXP/N[2] チャネル選択及びRead

#(CYC*5) jtag_set_dr({2'bxx,4'b0010,10'h040,16'h0012});

#(CYC*5) jtag_set_dr({2'bxx,4'b0001,10'h012,16'hXXXX});

#(CYC*5) jtag_set_dr({2'bxx,4'b0000,10'h012,16'hXXXX});

// Finish simulation

#(CYC*10) $finish();

end

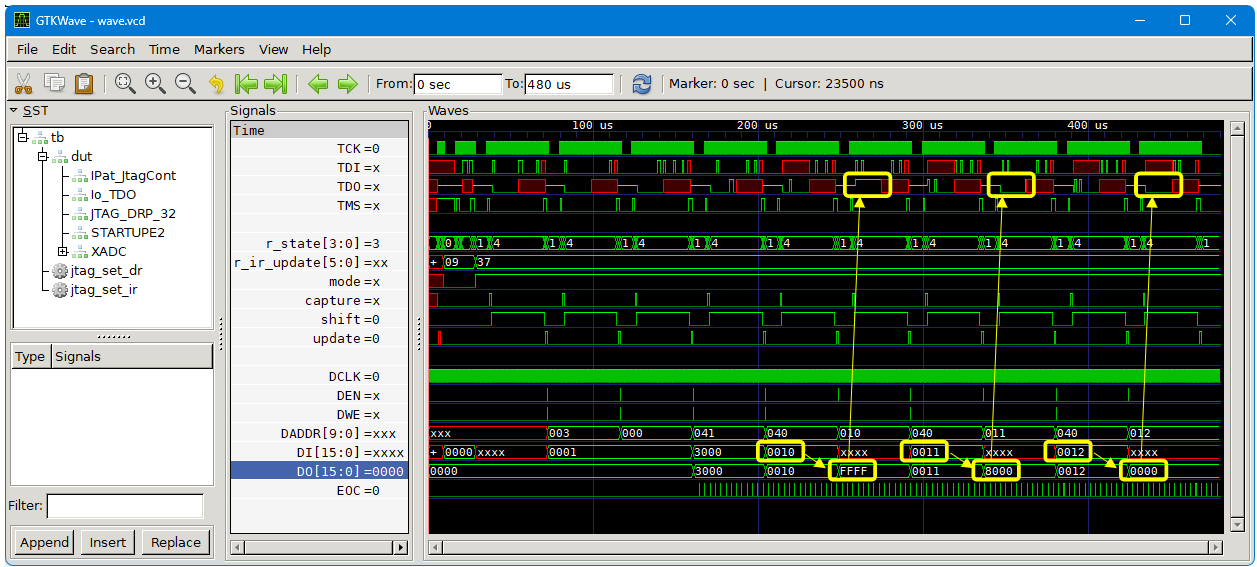

Simulation波形

- topモデルとテストベンチが揃えば、後はSimulationです。Simulationにはiverilogを使っています。ファイルやオプション指定等は、こちらの Makefile を参照ください。

- Simulation実行結果の波形が下記です(クリックで別タブへ拡大表示します)。

- アドレスh40にReadチャンネル(16'h0010 = VAUXP/N[0])を設定後、次のJTAG Sample/PreloadでCapture→Shift Outしているのがわかりますね(TDO Shift OutはLSBから出てきます)。

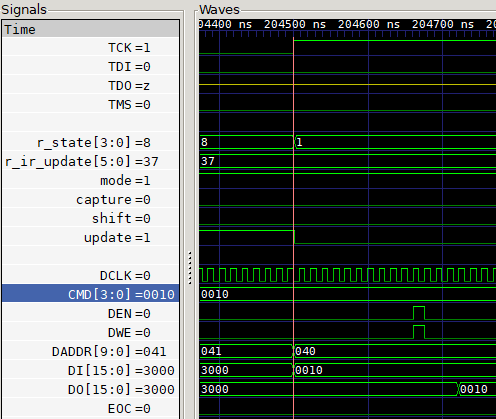

- Arbitrator(疑似Wait)の動作を見てみましょう。下記はJTAG Update部の拡大波形です。

- update(=xadc_update)信号はTCKの同期信号です。JTAG DRP内のupdate-FFへ値が転送された後update信号が立ち下がります。この立ち下がりをDCLKのシンクロナイザ経由で拾い、Arbitrator(疑似Wait)のリセットを解除します。

- 後はCMD[3:0]にセットされた値に従ってDEN/DWEのパルスを生成します。シンクロナイザを入れてDCLK 11cyc後にDEN/DWEが変化しています。

最後に

- XADCのレポートは今回で最後になります。あちこち浮気していたため時間かかってしまいました。まだ実際のFPGAで試すことができていないので、試行後にフィードバックあれば追記したいと思います。

- 実際のところ、DCLKに内部OSCを使っているため、周波数がかなり不安定でしょう。分周比を大きくして影響を小さくするとともに、TCKとの比率を考慮して十分なマージンを確保したタイミング/レートの設定が必要でしょう。

- XADCのJTAG制御について調べる前はIEEE 1500的なものかと思っていましたが、違っていたのは意外でした。このあたりは過去資産との関係があるのかもしれないのと、内部テストや制御の必要性がFPGA/CPLDではアピールポイントにならないことも影響しているのかなと考えています。

Copyright(C) 2024 Altmo

本HPについて

本HPについて