2024/08/03

- 前回までXADCをDRPから直接制御していましたが、今回からJTAG経由の制御へ移ります(*1)。XADCをJTAGで利用する際に考慮する点を列挙してみました。

- チェーン選択のIR = 6'b110111

- アクセス先は32bit JTAGチェーン

- JTAG DRP Update後にDCLK 10cycが必要

- リセットはRESETポートではなくXADC JTAG RESETを使う

- JTAGLOCKEDの設定

- FPGA configuration前のVAUXP/N有効化

- XADC自身はDCLKで動作するため、JTAGとDCLK間の非同期制御を行うArbitratorがいます。ただし、このArbitrator回路の具体的なモデルは不明なため、先に挙げた "DCLK 10cyc" の制約を意識しつつ自力でモデル作成することになります。

JTAGコントローラ改造

- まずはIR=6'b110111で、XADCの32bitチェーンにアクセスするJTAGコントローラを作成しますが、これは以前JTAG Boundary Scanを扱った際に作成したJTAGコントローラにちょっと機能追加します。

- 追加の内容は下記です

- xadc_si(output), xadc_so(input)ポートの追加

- xadc_capture, xadc_shift, xadc_update, xadc_modeポートの追加

- IR=6'b110111の時、制御対象チェーンをxadc_si/xadc_soとする論理追加

- そして作成したのがこちらの IPat_JtagCont.v になります(*2)。変更点については以前のRTLとWinMerge等で比較するとわかりやすいかと思います。

JTAG DRPチェーンとArbitrator

- 全体モデル作成の前に、JTAG DRPチェーンの内容を見てみましょう。下記は公式ドキュメントからの抜粋図です。

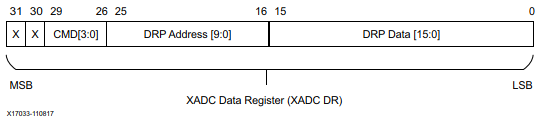

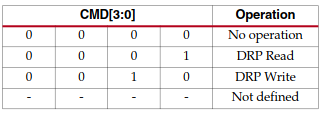

- [15:0]がDRP Data, [25:16]がDRP Address。DEN/DWE相当はありませんが、代わりCMD[3:0]が[29:26]にあります。

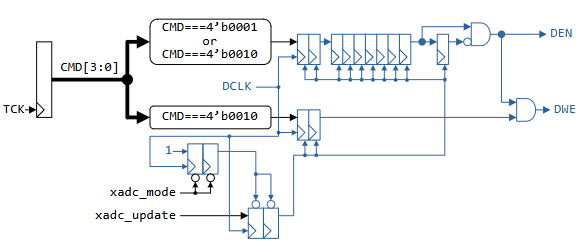

- 先程Arbitrator回路モデルを自力作成すると書きましたが、上記のコマンドをデコードしてDEN/DWE信号を生成し、DCLKに乗せ換えてパルス生成する回路をJTAG DRPチェーンとXADCの間へ入れることになります。

- 手抜きですが下記のような回路です。xadc_mode==0で非同期リセットし、解除時にDCLK同期化します。後はxadc_updateが入るたびにデコード出力系をリセットします。xadc_modeとxadc_updateはレーシングしない前提の回路です(*3)。

- あとは、32bitのJTAG DRPチェーン本体ですが、これはBC_1セルを32個つなげれば良いですね。

Figure 1: XADC JTAG DRPチェーン(XADC資料より抜粋)

Table 1: JTAG DRPコマンド(XADC資料より抜粋)

Figure 2: JTAG DRP 簡易Arbitrator

Simulationモデルの全体

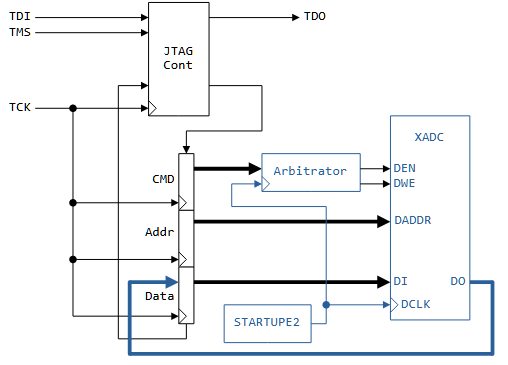

- これで要素は揃ったので、全体のモデルをラフに作ると下記のようになります。

- DCLKはDRP Simulationと同様にSTARTUPE2から供給します。

- 外部ポートはJTAGのTAPのみです。XADCのAUXアナログ入力ポートもモデル中にありませんが、Simulationでは design.txt からアナログ値を与えるので外部アナログポート作成は特に必要ありません。

- 次回は、実際に作成したモデルでJTAG DRP Simulationを行います。

Figure 3: JTAG DRP Simulationモデル全体

- JTAG制御について知識がある前提です。JTAGについてよく知らない場合は以前のレポートを参照下さい。

- 今回はモデル作成をして組み上げるところまでなので、次回の動作確認中にミスあれば修正します。

- 非同期回路として作っていないのでご注意を。xadc_modeとupdateは本来TCK同期論理の中で使用する信号です。FF出力ではなく論理を経由しているので、非同期であること以外にグリッチも乗る可能性あります。

2024-08-13: 簡易Arbitrator回路修正(NOP不必要としました)

Copyright(C) 2024 Altmo

本HPについて

本HPについて