2019/10/05

- 今回はPLLを扱います。なぜPLLが発振するのか(*1)という話には触れず、「そこにPLLのIPがある」そして「使うにはどう設定すれば良いのか」という観点でレポートします。

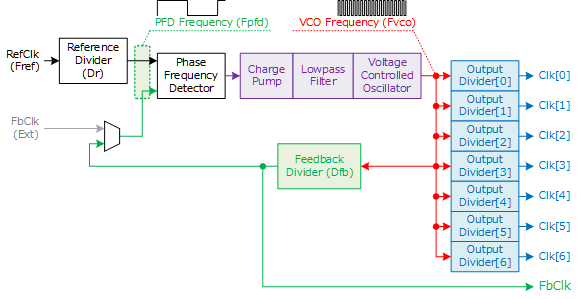

- まずはPLLのブロック図を見てみましょう。XilinxのPLL(*2)を参考に書いています。、他のベンダ...ALTERA(Intel)/Silicon Creations等も考え方は同じです。PLLを設定するには、アナログ的理解を除いたとしても、下記図は頭に入っている必要があります。

- PLLは入力クロック(RefClk)をVCOで逓倍して高周波($F_{vco}$)を作ります。周波数を安定させるためにフィードバック経路(緑線)があり、FvcoをFeedback Dividerで分周して元の周波数($F_{pfd}$)に戻し、Phase Frequency Detector(PFD)へ送ります。

- PFDは入力周波数とフィードバック周波数を比較し、その比較結果に従ってVCOを制御します。

- Fvcoが想定通りの値になれば、PFDに入る入力クロックとフィードバッククロックの周波数が一致し、そこで安定状態になります。「PLLがロックした」とはこの状態を指します。よってPLLロック時は下記が成立します。PLLの設定とはPLLが満たす仕様を考慮しつつ、下記が成立する条件を決めることなのです。

Figure 1. PLL ブロック図

| $\displaystyle F_{pfd} = \frac{F_{vco}}{D_{fb}}=\frac{F_{ref}}{D_{r}}$ | : PLLロック時の成立条件 |

| $F_{pfd}$ | : PFD入力周波数 | |

| $F_{vco}$ | : VCO周波数 | |

| $D_{fb}$ | : Feedback divider分周値 | |

| $F_{ref}$ | : RefClk周波数 | |

| $D_{r}$ | : Reference divider分周値 |

まずはVCO周波数を決める

- まず最初に考えるのはVCOの周波数($F_{vco}$)です。1個のPLLから複数の周波数を出力したい場合ですが、$F_{vco}$は最も高い出力周波数($F_{outmax}$)の整数倍(*3)として候補が決まります。

- 例えば $F_{outmax}$が1250[MHz]の場合、$F_{vco}$の候補は下記のようになります。

- PLLマクロのカバーするVCO周波数範囲が 1000[MHz] 〜 3000[MHz] だった場合、$F_{vco}$の候補は下記に絞られます。

-

$F_{outmax} \times 1$ = 1250[MHz]

$F_{outmax} \times 2$ = 2500[MHz]

$F_{outmax} \times 3$ = 3750[MHz]

$F_{outmax} \times 4$ = 5000[MHz]

...

-

$F_{outmax} \times 1$ = 1250[MHz]

$F_{outmax} \times 2$ = 2500[MHz]

出力周波数とVCO周波数の組み合わせ

- $F_{oumax}$以外の出力周波数を作ることができるかをチェックします。例えば 1250[MHz], 125[MHz], 100[MHz], 166.67[MHz]を出力したい場合、各周波数の出力分周値は下記となります。

- 上記表からわかるように、整数分周で要求する出力周波数を作れるのは $F_{vco}$=2500[MHz]です。周波数の組み合わせによって、$F_{vco}$候補が複数存在することもありますが、その場合は、一般的に下記を基準に判断します。

- 入力周波数 $F_{ref}$, $F_{pfd}$の整数倍で、$F_{vco}$を作れること(次で説明)

- PLLのVCO周波数カバー範囲の中央(*4)に近いこと

| 出力周波数[MHz] | 分周値($F_{vco}$:1250MHz) | 分周値($F_{vco}$:2500MHz) |

| 1250 | 1 | 2 |

| 125 | 10 | 20 |

| 100 | 12.5(NG) | 25 |

| 166.67 | 7.5(NG) | 15 |

Reference/Feedback Dividerの値を決める

- PFD入力周波数($F_{pfd}$)のPLLマクロ仕様を確認します。今回は10〜200MHzが仕様だとします。$F_{vco}$をFeedback Divider($D_{fb}$)で落とすので、この場合は下記が範囲になります。

- 入力周波数($F_{ref}$)が 66.66MHzだった場合、$F_{pfd}$ は $F_{ref}$の整数分周($D_{r}$)として決まります。更に$F_{pfd}$と$F_{vco}$の分周比($D_{fb}$)が整数であるものを探します。今回は下記表のように$D_{r}$=2, $D_{fb}$=75になりました。

-

$D_{fb}$ = 250 〜 13

| $F_{ref}$[MHz] | $D_{r}$ | $F_{pfd}$[MHz] | $D_{fb}$ | $F_{vco}$[MHz] |

| 66.66 | 1 | 66.66 | 37.5(NG) | 2500 |

| 2 | 33.33 | 75(OK) | ||

| 3 | 22.22 | 112.5(NG) | ||

| ... | ||||

Digital設定をまとめ、Charge pumpとLowpass filterの設定を確認する

- 得られたPLLのDigital設定をまとめました。赤字は要求仕様、青字は設定値、緑字はPLLマクロ仕様です。

- FPGA PLLの場合、Charge pump, Lowpass filterへの設定はPLL IP内で決められるので特に気にする必要はありませんが、ASIC系の場合サポートを受けることが可能であれば上記表を渡した上で推奨設定値を教えてもらうか、任意設定値に変更できるよう設計を行うとトラブル(*5)を避けられます。

| $F_{out}$[MHz] | $D_{out}$ | $F_{vco}$[MHz]: (1000〜3000) |

$D_{fb}$ | $F_{pfd}$[MHz]: (10〜200) |

$D_{r}$ | $F_{ref}$[MHz] |

| 1250 | 2 | 2500 | 75 | 33.33 | 2 | 66.66 |

| 125 | 10 | |||||

| 100 | 25 | |||||

| 166.67 | 15 |

2019-10-06 : Div値typo修正

2019-10-13 : PLL設定まとめにDout追加

Copyright(C) 2019 Altmo

本HPについて

本HPについて