2015/11/29

- 今回は作成した回路の検証を行いました。結果から言うと接続ミスがあったためRTLを修正しています。こちら「ecc_064_2015_0170a.v」を参照下さい。

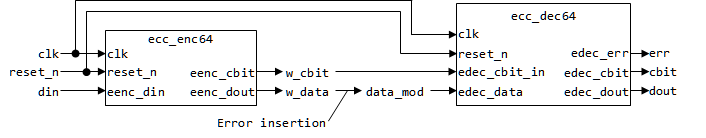

- 下記が、今回作成したテストベンチ「tb.v」の構成になります。

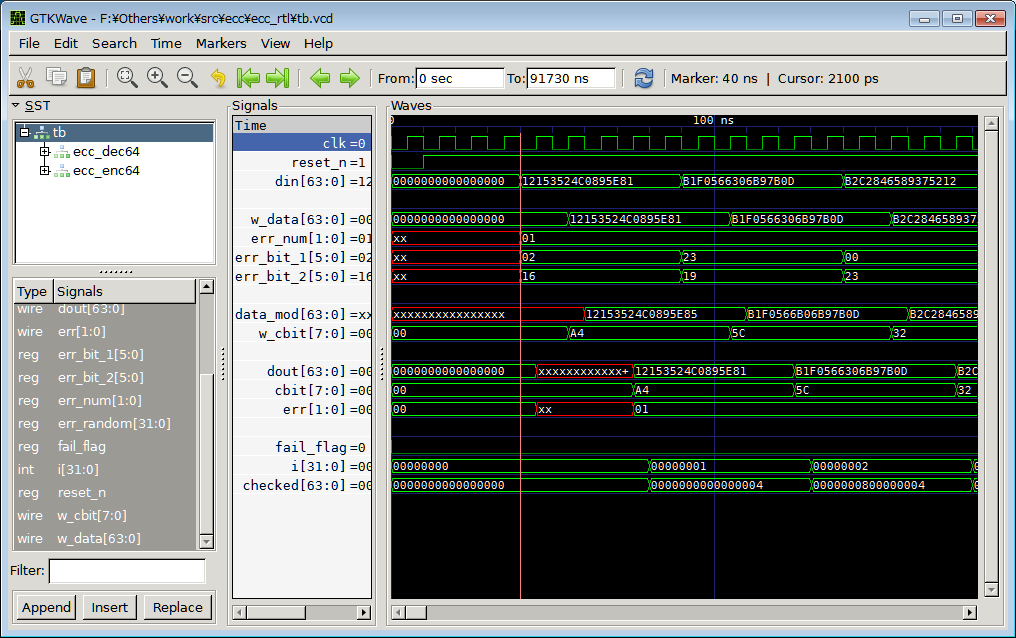

- データ入力 din への値は乱数です。そしてECCエンコード後にエラーを挿入しますが、挿入の数(0〜2)、挿入対象bit(0〜63の何れか)も乱数で決めています。

+ err_num[1:0] : エラー個数(0〜2)

+ err_bit_1[5:0] : エラー挿入bit(0〜63) 1個目

+ err_bit_2[5:0] : エラー挿入bit(0〜63) 2個目

- エラー挿入されたデータを、ECCデコード後にチェックし、PASS/FAILを判定します。

+ エラー挿入0 : (din == dout == data_mod) and (err == 2'b00)

+ エラー挿入1 : (din == dout != data_mod) and (err == 2'b01)

+ エラー挿入2 : (din != dout == data_mod) and (err == 2'b10)

- 全てのbitで、ECCの訂正動作が確認されるまで、ループ実行し続けます。尚SimulatorはIcarus Verilogを使用しました。

iverilog tb.v ecc_064_2015_0170a.v

vvp a.out > sim_result.txt

実行結果

- 実行結果はもちろんPASSになっています。こちら「sim_result.txt.zip」実行結果のログになります。ログ中左端の文字列は

+ 0E0C : エラー挿入無し

+ 1E1C : エラー挿入1bit, 訂正1bit

+ 2E0C : エラー挿入2bit, 訂正無し

を意味しています。右端の「e1:〜 e2:〜」はエラーが挿入されたbitです。 - 下記が、Gtkwaveで観測した波形です。全体のVCDファイルはこちら「tb.vcd.zip」になります。

- 32bitや128bitのECC回路が必要になった際も、同様な手順で作成/検証を行うことになります。

おまけ

- 今回の回路では、ダブルエラー検出のために、全データbitをEORする方式を取っています。一番簡単に理解できることが理由ですが、これだとデータ幅が広くなった時に論理が深くなり、メモリ出力データのタイミングパスにおけるボトルネックになってしまいます。

- これはParityビットの計算論理段数を揃える観点でも効いてきます。これについては書いて良いかどうか迷いがあるため、ヒントだけに留めます。各データに対応するシンドローム表にて1の数に着目して下さい。全部奇数とした場合どうなるか。

Copyright(C) 2015 Altmo

本HPについて

本HPについて